LAPORAN AKHIR 1

Modul 3: Percobaan 1

1. Jurnal[Kembali]

2. Alat dan bahan[Kembali]

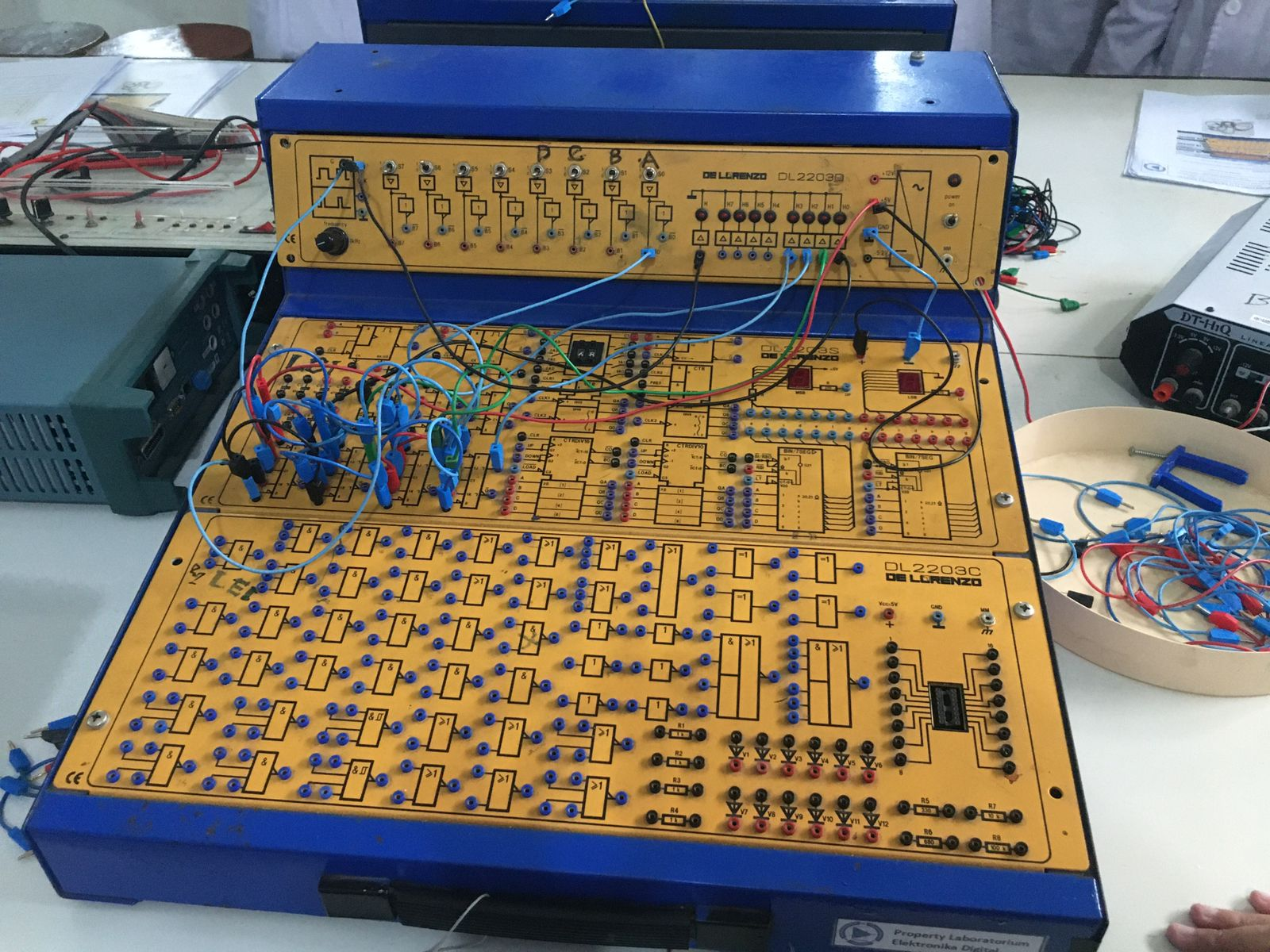

A. Alat dan Bahan (Modul De Lorenzo)

1. Jumper

B. Alat dan Bahan (Proteus)

1. IC J-K Flip Flop (74LS112)

Kelebihan JK Flip-flop adalah tidak adanya kondisi terlarang atau yang berarti di beri berapapun inputan asalkan terdapat clock maka akan terjadi perubahan pada keluarannya / outputnya. berikut adalah symbol dan tabel kebenaran dari JK Flip-Flop.

2. Power DC

|

3. Switch (SW-SPDT)

4. Logicprobe atau LED

3. Rangkaian Simulasi[Kembali]

4. Prinsip Kerja[Kembali]

Pada percobaan 1 digunakan Asynchronous Binary Counter 4 bit dengan 4 buah J-K flip flop. Jika

input T- flip flop (input J dan K yang disatukan) pada JK flip flop dihubung

ke power, maka output IC akan mengalami kondisi toogle. Tetapi, jika JK flip flop input clock yang dihubungkan clock maka output toogle pada masing-masing IC akan berubah sesuai dengan keadaan

aktifnya, yaitu aktif saat fall time.

Jika clock dalam kondisi fall time, maka output flip flop pertama akan

berubah outputnya menjadi 1, sedangkan pada flip flop

kedua tidak terpengaruh apapun karena input clock kedua diperoleh

dari output flip flop pertama. Akibatnya, clock flip flop kedua dalam kondisi

rise time sehingga outputnya adalah 0. Begitupun seterusnya

pada ke tiga dan ke empat sehingga diperoleh outputnya secara bergiliran dan bergantian

mengalami kenaikan atau penurunan pada outputnya.

1. Analisa apa yang terjadi pada rangkaian percobaan 1 ketika input SR nya dihubungkan ke ground (ke low atau SR active low)?

Jawab:

Ketika input SR dihubungkan ke ground yang mana SR active low sehingga menyebabkan output Q dan Q’ menjadi bernilai 1 sehingga menyebabkan clock pada flip-flop tetap berada pada kondisi toggle dikarenakan hanya menerima input 1 dari output flip-flop sebelumnya dan menyebabkan bilangan biner yang dihasilkan pada semua flip-flop.

2. Apa yang terjadi saat output Q masing-masing flip-flop dihubungkan ke input clock flip-flop selanjutnya?

Jawab:

Output Q merupakan kebalikan dari output Q’ yang mana ketika output Q bernilai 0 maka Q’ akan bernilai 1. Dari sana baru kita lihat bahwa ketika rangkaian dijalankan maka output Q pada semua flip-flop akan bernilai 1 dikarenakan semua output Q bernilai 0. Sehingga biner yang dihasilkan adalah 1111 atau 15, dan ketika clock output flip-flop pertama akan menyebabkan bilangan biner yang dihasilkan adalah 0001 atau 1 begitu seterusnya.

7. Download[Kembali]

Download HTML [disini]

Download Video Percobaan [disini]

Download Datasheet IC 74LS112 [disini]Download Datasheet Switch [disini]

.png)

Tidak ada komentar:

Posting Komentar